IBM, en asociación con Samsung, GlobalFoundries y SUNY Poly CNSE, ha desarrollado un chip de 7 nanómetros. Así es como cambiará los materiales y procesos en la fabricación de semiconductores.

Si tuviéramos que pensar en los dispositivos electrónicos como moléculas, el semiconductor sería el átomo, y los cambios en estos bloques de construcción a menudo tienen enormes implicaciones para el futuro de la tecnología en su conjunto.

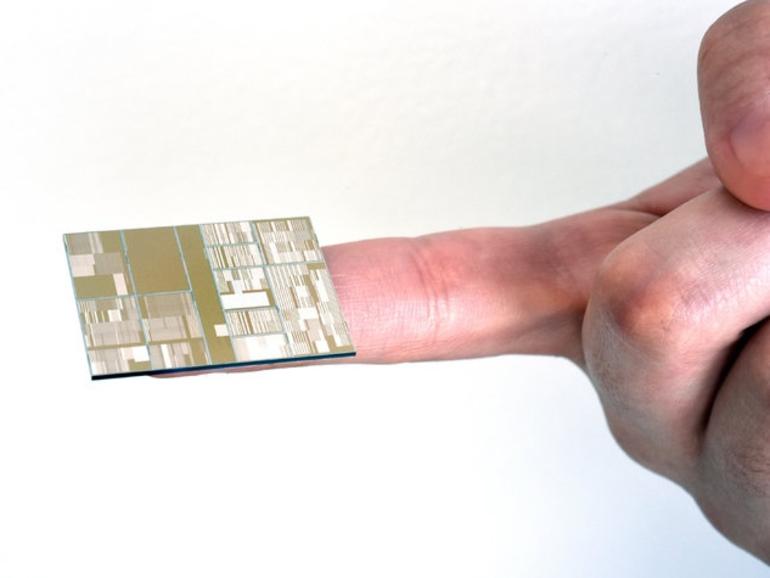

El jueves 9 de julio de 2015, IBM Research anunció la producción de un chips de prueba de nodos de 7 nm con transistores en funcionamiento. IBM, Samsung, GlobalFoundries y los Colegios de Ciencia e Ingeniería a Nanoescala del Instituto Politécnico de SUNY (SUNY Poly CNSE) participaron en el desarrollo de la tecnología, que podría permitir hasta 20 mil millones de transistores en un chip del tamaño de una uña humana.

«La producción principal de la mayoría de las piezas es de 22nm en este momento», dijo el analista de Forrester Richard Fichera. «Hay una producción temprana de piezas de 14nm ahora, y más de las que saldrán a la venta a finales de este año. 10nm comenzará a llegar el próximo año[con] entregas anticipadas. Y, 7nm es un ciclo más allá de eso, así que están saltando el siguiente ciclo de producción.»

Típicamente, dijo Fichera, los semiconductores hacen la transición en aproximadamente uno sobre la raíz cuadrada de dos, lo que significa que se contraen en aproximadamente un 30% y dan el doble de transistores por área. El hecho de que IBM haya sido capaz de producir un chip que funcione a 7 nm significa que ha pasado por alto la ley de Moore en el ciclo de desarrollo.

Ahora, probablemente no veremos chips de 7nm en producción muy pronto, pero este anuncio sigue siendo un hito. Según Michael Liehr, vicepresidente ejecutivo de innovación y tecnología de SUNY Poly CNSE que trabajó en el proyecto, el ciclo de desarrollo desde la concepción más temprana hasta un chip listo para la producción podría durar de 7 a 10 años, y cada paso duraría de un año a un año y medio.

«Ahora es un proceso establecido que se ha demostrado que produce algo», dijo Liehr. «Pero, los siguientes pasos a lo largo de la línea serían asegurarse de que se puede hacer repetidamente y mejorar la calidad del proceso y añadirle más características y detalles».

Liehr dijo que probablemente pasarían otros dos o tres años antes de que los chips de 7 nm estén completamente listos para su fabricación.

Hay dos cambios clave que permitieron la producción de los transistores de este tamaño. La primera innovación fue el uso de transistores de canal de Silicio Germanio (SiGe. El germanio se mezcla con el silicio en forma de aleación. El átomo de germanio es más grande que el silicio, dijo Liehr, así que cuando se mezcla, se expande y ejerce presión sobre el silicio circundante.

«Esa presión es en realidad muy útil para conseguir cambios en la velocidad a la que los portadores atraviesan el silicio», aseguró Liehr.

Esto ayuda a mejorar el rendimiento del dispositivo, que se incrementó en un 50%. La mezcla se ha utilizado durante un tiempo para los contactos de semiconductores, pero este es el primer caso en el que la mezcla de germanio y silicio se ha utilizado en el camino actual.

El segundo cambio es el uso de la litografía ultravioleta extrema (EUV) para crear los chips, que es el principal impulsor de la escala más pequeña. Tradicionalmente, los chips se fabrican utilizando litografía UV, también conocida como fotolitografía.

«Si usted tiene un VUE en funcionamiento, significa que puede hacerlo con menos pasos de litografía», dijo Fichera.

Menos pasos podrían significar un menor costo de fabricación, pero el costo de herramentalizar EUV podría anular esos ahorros de costos, especialmente en los primeros días, dijo Fichera. Sin embargo, el uso de EUV podría llevar a la reorganización de toda la industria, ya que EUV permite una mayor reducción de los chips.

Hay una posible desventaja, dijo Fichera, ya que un posible reequipamiento podría costar miles de millones de euros y podría llevar a una mayor consolidación de la cadena de fabricación, ya que sólo los principales actores en el espacio podrían permitirse el lujo de reequipar sus instalaciones de fabricación.

Según un comunicado de prensa de IBM, la empresa considera que la computación en nube, los grandes sistemas de datos, la computación cognitiva y los productos móviles son objetivos probables de la nueva tecnología. En cuanto a la movilidad, el nuevo chip es importante porque puede ayudar a los dispositivos a conservar el rendimiento y reducir el consumo de energía, o mejorar el rendimiento con la misma duración de la batería.

«Típicamente, lo que los proveedores de telefonía celular harán es una especie de mezcla de estos», dijo Liehr. «Proporcionan características adicionales, pero también aprovechan el menor consumo de energía para conseguir una mayor duración de la batería».

La baja potencia será el gran campo de batalla, dijo Fichera, con la mayor batalla entre Intel e IBM. Añadió que los dispositivos de tipo IO serán un caso de uso crítico para el pequeño tamaño y la baja potencia. Además, hay potencial para aplicaciones de sistema en un chip (SOC), que Fichera describe como: «La idea de que, además de la CPU, también tienes memoria y otros elementos lógicos en el mismo chip.»

En el chip de 10nm de IBM, la compañía dijo que era posible poner D-RAM en el chip. Si eso es posible en el chip de 7 nm, es mejor que se preste a la posibilidad de SOC.

En general, Fichera cree que esta es una buena noticia para todos en la industria, ya que podría acelerar el desarrollo para llegar al siguiente ciclo de desarrollo. Sin embargo, ese empuje va a estimular un nuevo nivel de competencia entre los gigantes de los semiconductores.

«El drama será genial, y espero que Intel dispare un tiro pronto como respuesta. No pueden dejar esto sin respuesta», dijo Fichera. «Será interesante ver lo que tienen que decir.»